发布时间:2022-12-22

当摩尔定律逼近极限,先进封装正成为后摩尔时代提升芯片性能的方式之一,并扮演重要角色。

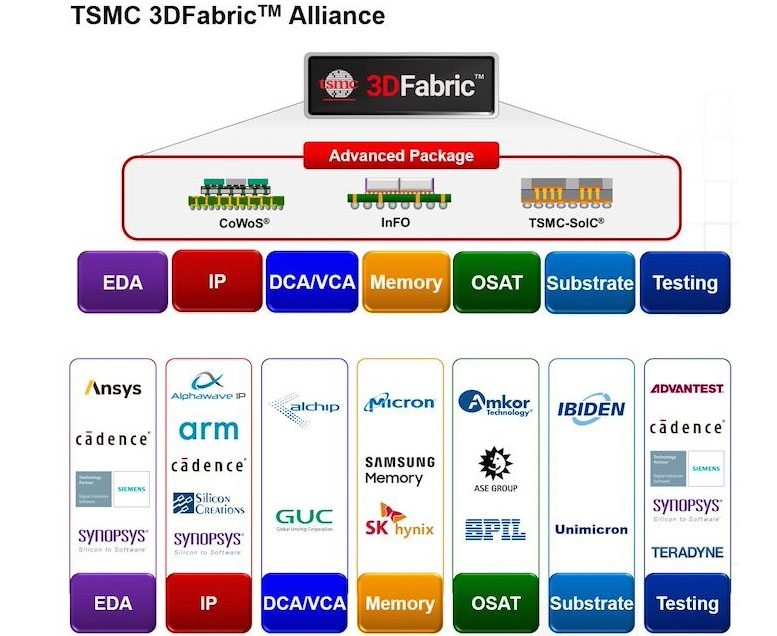

日前,台积电宣布正式成立开放创新平台3D Fabric联盟,旨在协助客户达成芯片及系统级创新的快速实作,并且采用台积电由完整的3D硅堆迭与先进封装技术系列构成的3D Fabric技术来实现次世代的高效能运算及行动应用,推动3D半导体发展。

截止发稿,已有包括美光、三星记忆体、SK海力士等在内的19个合作伙伴同意加入,主要涵盖EDA芯片设计自动化、IP知识产权、DCA/VCA合同芯片设计、Memory存储芯片制造等环节。据悉,这一联盟是台积电第六个开放创新平台(OIP)联盟。

其实,台积电早在2012年便已开始在封装领域布局,并于2020 年将旗下 SoIC、InFO 及 CoWoS 等 3D IC 技术平台进行整合,并命名为“3D Fabric”。在平台的牵引下,台积电开始积累在2.5D/3D封装技术领域的实力,并运用到实际场景中。

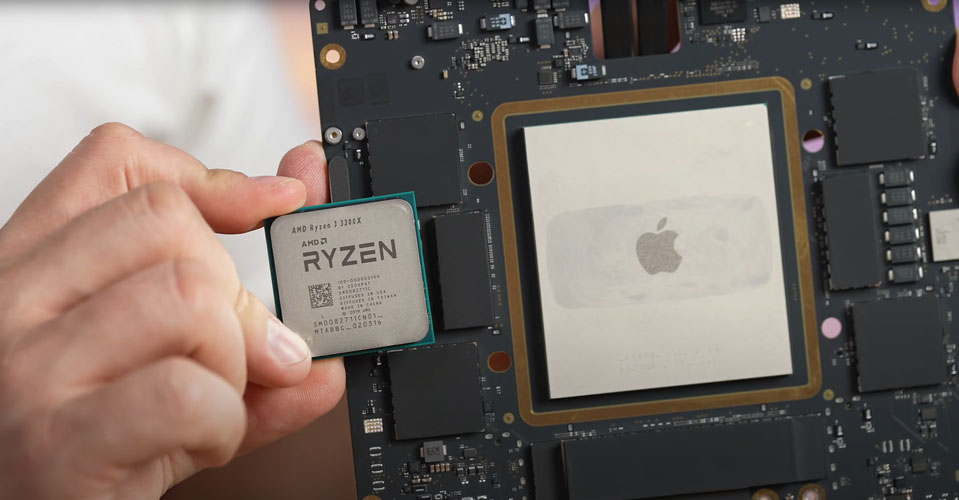

比如采用2.5D的InFO-LSI 封装技术将苹果公司两颗M1 MAX芯片制造成完整的M1Ultra,实现2.5TB / s 的带宽。以及运用3D SoIC-WoW封装工艺,为客户制造集成600亿根晶体管的7nm芯片。

这些采用先进封装工艺的芯片都有一个特点,那就是晶体管数量实现翻倍。M1 MAX单颗芯片的晶体管数量为570亿根,而M1 Ultra的晶体管数量升级到了1140亿根,CPU核心更是增加到20个。也正是基于这样的深厚技术积累,台积电才能牵头成立3D Fabric 联盟。

那么先进封装会成为行业发展趋势吗?答案显而易见。

自1965年摩尔定律被提出后,半导体行业便一直遵循其轨迹高速发展。但近年来随着5G、物联网、大数据、AI智能制造等技术的不断突破创新,半导体先进制程不断往7nm/5nm,甚至以下迈进,摩尔定律在2D芯片微缩上的技术挑战越来越多,成本与开发时间均呈现跳跃式的增长。而通过Chiplet、异质整合、3D 堆叠技术,则可替摩尔定律“续命”。因此封装技术渐渐由传统封装走向先进封装,朝系统级、晶圆级等先进封装技术迈进。

而随着英特尔、三星、台积电、日月光、安靠、长电科技等前后道头部厂家凭借各自优势入局,先进封装已成必争之地。以长电科技、通富微电、华天科技为代表的国内封测头部厂家通过自主研发和兼并收购,已基本形成先进封装的产业化能力,并在Bumping、Flip-Chip、TSV和2.5D/3D堆叠技术等关键技术上实现了与国际领先企业对标的能力。

值得一提的是,因先进封装推动前后道工艺相互渗透融合分化出的“中道”概念,或许将成为行业新模式。

综上所述,先进封装技术目前已经成为半导体产业创新、向前再推进的重要关键,继续推动产业参与者探索新领域,同时也进一步成为弥合IC芯片、PCB之间发展差距的重要关键。对此,深科达半导体作为业界领先的测试分选机一站式解决方案提供商,定当不断精进自己的技术和服务,推出兼具高性价比、高集成度、高密度互联和高可靠性的解决方案,助力先进封装迈向新高度。

深圳市深科达半导体科技有限公司 Copyright 2021

技术支持:【东莞网站建设】