发布时间:2022-12-22

芯片的产生会经过芯片设计、晶圆制造和封装测试几个大的环节。实际上在设计阶段,芯片有完备的验证流程,仿真验证、UVM、形式验证以及基于FPGA的系统级验证(SLE,System Level Emulation)等验证手段可以保证100%设计功能正确性。一般来说芯片能够进行到流片阶段,芯片的netlist是经过了所有测试用例的验证,完美实现设计需求的。所以,半导体的测试重点就是要针对制造过程进行检测、验证。

芯片的制造过程极度复杂,每一步都有可能带来误差从而影响最终的良率,因此在关键的制程环节,都会加入测试过程。行业内基于半导体制造过程工艺及产业链的分工,将芯片制造过程划分为前道制程和后道制程,相应的测试也分为前道测试和后道测试。

一 、前道测试

前道制程主要是晶圆制造的过程,是在硅片上多次进行进行涂膜、曝光、显影、蚀刻、离子植入、金属溅镀等环节,最终形成多层电路交叠的集成电路。

因此,前道测试的对象就是工艺过程中的晶圆,主要测试内容总体上可分为两个方面:

1、量测类,主要量测芯片制程尺寸、材料性质等,如膜厚度量测、OCD尺寸量测等

2、检测类,主要检测芯片杂质颗粒、表面机械划伤、晶圆图案缺陷等

前道测试涉及的技术主要包括材料、光学、微观物理、化学等多个方面,相应的测试设备包括膜厚量测设备、OCD关键尺寸量测设备、光刻校准量测设备、图形缺陷检测设备等。

二.后道测试

后道制程从收到一盘包含成百上千个排列整齐的Die的Wafer开始,主要工序就是对Die进行切割、引线键合、封装,整个过程从CP测试开始、以FT测试完成作为结束。

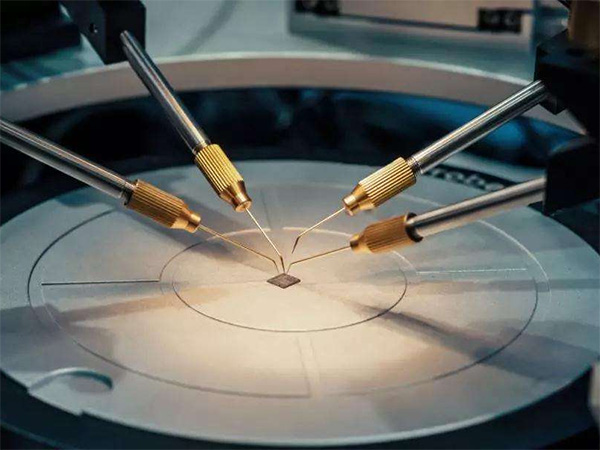

CP测试,也称为晶圆测试,测试对象是针对整片wafer中的每一个Die,目的是验证整片wafer中的每一个Die是否都能基本满足芯片的特征或者设计规格书。直白的说就是对送入的Wafer进行验收测试,避免不达标的Die进入封装环节,减少封装成本浪费。测试项主要针对功能和电性参数的验证。

FT测试是芯片出厂前的最后一道拦截。FT测试的对象是封装后的芯片,主要目标是避免在Wafer切割时导致损伤或者切割后引线键合异常的芯片直接流出。FT测试的主要测试内容也是功能和电性参数测试。

值得注意的是,CP测试和FT测试的测试项目是类似的,他们的测试仪表有些甚至可以是同一种,但因测试对象处于芯片不同阶段,装载连接方式不同,所以需要不同的配套设备。那么作为核心部分的测试仪表要执行的功能测试与电性测试,具体要测试哪些内容呢?一般主要包含三个方面的测试:

DC参数测试:主要是针对各种情况下的电压、电流参数进行测量,验证芯片是否符合设计规范,如开短路、漏电流等等。

AC参数测试:主要是针对时序相关指标进行测试,验证芯片是否符合设计规范,如传输延迟、信号上升/下降时间等等。

功能测试:主要针对芯片的逻辑运算、信号处理、控制、存储、发射等进行测试。

深圳市深科达半导体科技有限公司 Copyright 2021

技术支持:【东莞网站建设】